Specification

| T5L0 ASIC | Developed by DWIN.Massa productio in 2020,1MBytes nec Flash in thechip, 512KBytes ad usum datorum reponunt.Rewrite exolvuntur: super100,000 temporibus |

| Color | 18-bit |

| LCD Type | IPS, TFT LCD |

| Viewing Anglus | L/R/U/D) 85°/85°/85°/85°(L/R/U/D) |

| Propono Area(AA) | 71.9mm(W)* 70.2mm(H) |

| Resolution | 480*800 |

| Backlight | LED |

| splendor | DMG48480T040_01WTC:270nit DMG48480T040_01WTR:250nit DMG48480T040_01WN:300nit |

| Type | RTP (panel tactus resistens) |

| Structure | ITO velum + ITO vitrum |

| Modus tactus | Support punctum tactus et trahat |

| Superficies duritia | 3H |

| Lux Transmittance | Super LXXX% |

| vita | Plus 1,000,000 temporibus tactus |

| Type | CTP (Tange Capacative panel) |

| Structure | G+G compages cum superficiei tegumento Asahi vitreo temperato |

| Modus tactus | Support punctum tactus et trahat |

| Superficies duritia | 6H |

| Lux Transmittance | Super XC% |

| vita | Plus 1,000,000 temporibus tactus |

| Potentia Voltage | 6~36V |

| Operatio Current | VCC=12V, max backlight,135mA |

| VCC=12V, backlight off,55mA |

| Operatio Temperature | -20~70℃ |

| Repono Temperature | -30~80℃ |

| opus Umor | 10%~90% RH |

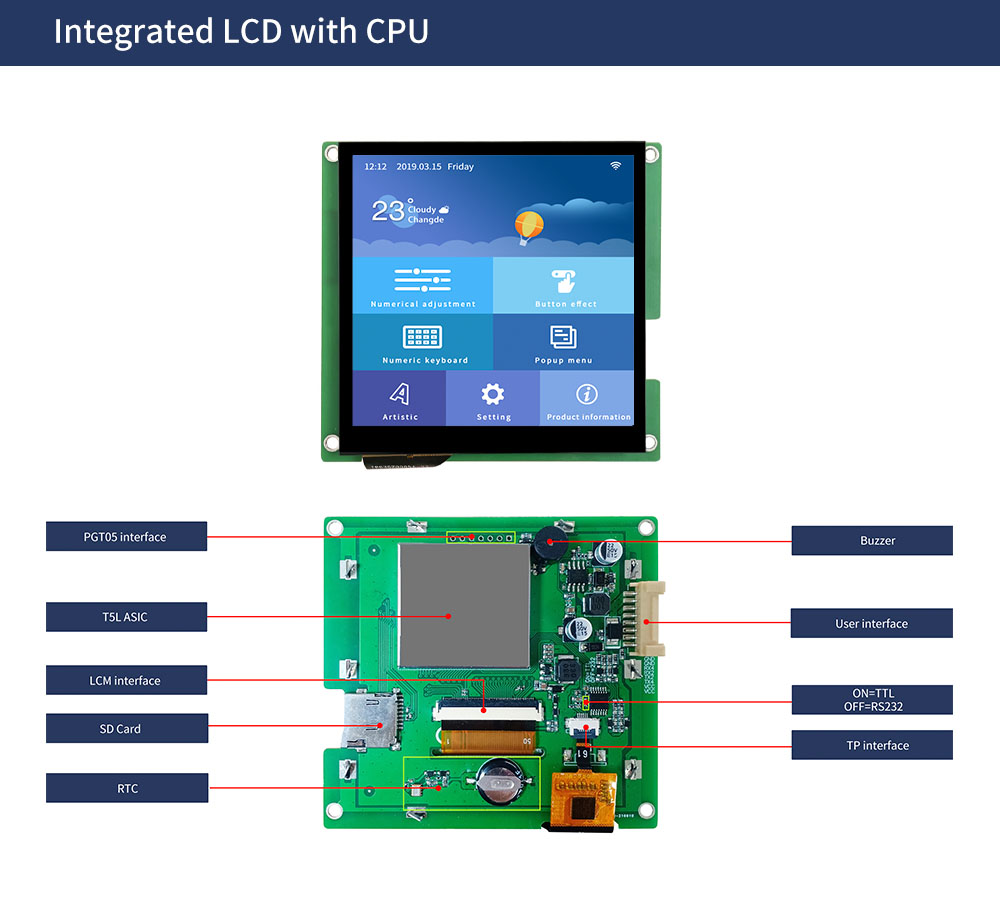

| LCM interface | FPC50_0.5mm, RGB interface |

| RTP interface | 4Pin_1.0mm interface |

| CTP interface | FPC6_0.5mm, IIC interface |

| Baud rate | 3150~3225600bps |

| Output intentione | Output I, Iout = 1mA; 3.0~ 3.3 V |

| Output 0, Iout = -1mA, 0~0,3 V | |

| Input intentione RXD) | Input 1,Iin = 1mA;2.4~5.0V |

| Input 0,Iin = -1mA; 0~0.5V | |

| User interface | 8Pin_2.0mm nervum ad copiam et communicationem vide.Download rate (valorem typicum): 12KByte/sUART2: ON=TTL/CMOS;OFF=RS232 UART4: ON=TTL/CMOS;Off=RS232 (tantum available post OS configuratione) |

| Expand Flash | 16MBytes NOR Flash, pro fontibus, imaginibus et imaginum audio.Rewrite cyclum: per 100,000 tempora |

| RTC | Super-capacitas pro potentia copia.Sagaciter: 1s/24h.Potest operari Northmanni ad XXX dies post defectum virtutis |

| SD interface | FAT32.Fasciculi ex SD interface in statistics exponi possunt.Download rate: 4Mb/s |

| PGT05 interface | Cum productum casu inruerit, PGT05 ad update DGUS uti potes nucleus ut productum reditus ad normalem |

| DMG48480T040_01WTC | Capacitive tactus panel, Buzzer |

| DMG48480T040_01WTR | Panel tactus resistens, Buzzer |

| DMG48480T040_01WN | Nulla tange panel, Buzzer |