Specification

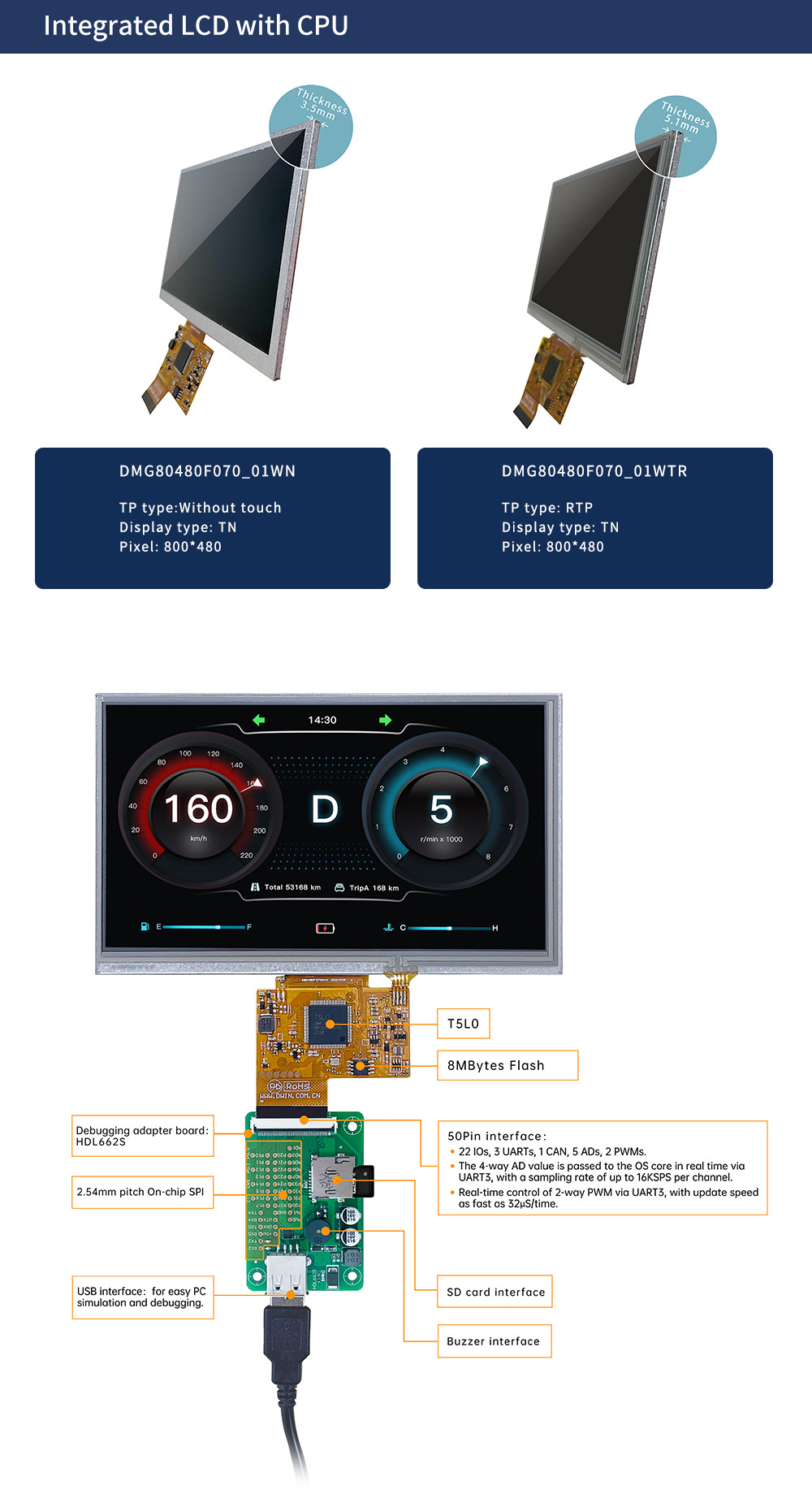

| T5L0 ASIC | Developed by DWIN.Massa productio in 2020,1MBytes nec Flash in chip, 128Kbytes variabilis repositionis spatium ad notitias permutandas cum OS CPU Core et memoria.Rewrite cyclum: per 100,000 tempora | ||

| Color | 262K colorum | ||

| LCD Type | TN, TFT LCD | ||

| Viewing Anglus | Normalis intuitus angulus, valor typicus 70°/70°/30°/40°(L/R/U/D) | ||

| Propono Area(AA) | 154.08mm (W) × 85.92mm (H) | ||

| Resolution | 800×480 | ||

| Backlight | LED | ||

| splendor | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| Type | RTP (panel tactus resistens) | ||

| Structure | ITO velum + ITO vitrum | ||

| Modus tactus | Support punctum tactus et trahat | ||

| Superficies duritia | 3H | ||

| Lux Transmittance | Super LXXX% | ||

| vita | Dotting > 1,000,000 times;Plaga 100,000 times;150g vi, retro egrediens quasi bis | ||

| Potentia Voltage | 3.6~5.5V | ||

| Operatio Current | VCC = +5V, Backlight on, 410mA | ||

| VCC = +5V, Backlight off, 115mA | |||

| Operatio Temperature | -10℃~60℃ | ||

| Repono Temperature | -20℃~70℃ | ||

| opus Umor | 10%~ 90% RH, valorem typicum 60% RH | ||

| Baud rate | 3150~3225600bps | ||

| Output intentione | Output 1, Iout = 8mA;3.0~3.3V | ||

| Output 0, Iout =-8mA;0~0.3V | |||

| Input intentioneRXD) | Input 1;3.3V | ||

| Input 0;0~0.5V | |||

| Interface | UART2: TTL; | ||

| UART4: TTL, ( Tantum available post OS configuratione | |||

| UART5: TTL, ( tantum available post OS configuratione | |||

| Data Forma | UART2: N81; | ||

| UART4: N81/E81/O81/N82;IV modos (OS configuratione) | |||

| UART5: N81/E81/O81/N82;IV modos (OS configuratione) | |||

| Socket | 50Pin_0.5mm FPC | ||

| Flash | 8M Bytes | ||

| PIN | Definition | I/O* | Eget Description |

| 1 | +5V | I | Virtutis copia, DC3.6-5.5V |

| 2 | +5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 input ADCs.12-bit resolutio in casu 3.3V potestatis copia.0-3.3V input intentione.Exceptis AD6, reliqua notitia in nucleum OS mittitur per UART3 in . verum tempus cum 16KHz sampling rate.AD1 et AD5 adhiberi potest parallelis, uti possunt AD3 & AD7 parallelis, qui sunt duobus 32KHz sampling AD.AD1, AD3, AD5, AD7 in parallelis adhiberi possunt, quodq aequalis a 64KHz sampling AD;notitia summatur MXXIV temporibus et deinde divisa per 64 ad valorem 64Hz 16bit AD obtinendum per oversampling. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3.3 | O | 3.3V output, maximum pondus 150mA. |

| 12 | SPK | O | EXTERNUS MOSFET ad stridorem vel oratorem repellere.Externus 10K resistor ut potentia illa deorsum deorsum trahatur. |

| 13 | SD_CD | IO | SD/SDHC interfacies, SD_CK coniungit capacitorem 22pF cum GND prope SD card interface. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | II 16 bis PWM output.Externus 10K resistor detrahi debet to terra ut potentia in humili gradu.Core OS in tempore reali per UART3 regi potest |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | Si RX8130 vel SD2058 I2C RTC utens ad utrumque IOs iungendum, SCL ad P3.2, & SDA ad P3.3 parallelis connexum. cum 10K resistor viverra-usque ad 3.3V. |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | Adhiberi potest externa 1 initus simul interrumpere, et sustinet utrumque humili intentione gradu vel ore trahens interrumpere modos. |

| 24 | P3.0/EX0 | IO | Adhiberi potest externa 0 initus simul interrumpere, et sustinet utrumque humili intentione gradu vel ore trahens interrumpere modos. |

| 25 | P2.7 | IO | IO interface |

| 26 | P2.6 | IO | IO interface |

| 27 | P2.5 | IO | IO interface |

| 28 | P2.4 | IO | IO interface |

| 29 | P2.3 | IO | IO interface |

| 30 | P2.2 | IO | IO interface |

| 31 | P2.1 | IO | IO interface |

| 32 | P2.0 | IO | IO interface |

| 33 | P1.7 | IO | IO interface |

| 34 | P1.6 | IO | IO interface |

| 35 | P1.5 | IO | IO interface |

| 36 | P1.4 | IO | IO interface |

| 37 | P1.3 | IO | IO interface |

| 38 | P1.2 | IO | IO interface |

| 39 | P1.1 | IO | IO interface |

| 40 | P1.0 | IO | IO interface |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | IO interface |

| 46 | P0.1 | IO | IO interface |

| 47 | CAN_TX | O | Can interface |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2(UART2 Vide portum OS core) |

| 50 | UART2_RXD | I |