--Shared from DWIN Froum

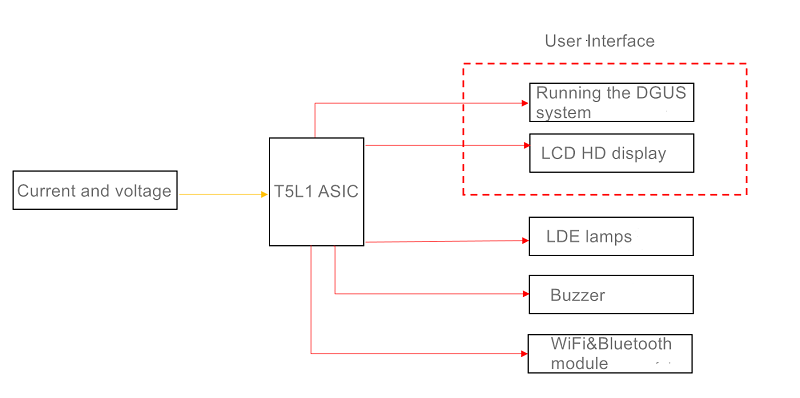

Usura DWIN T5L1 chip ut nucleus totius machinae imperium accipit et processus tactus, ADC acquisition, PWM informationes moderatur, et agit 3.5-inch LCD screen ut praesentem statum in reali tempore ostendat.Suscipe remotis tactus commensurationem lucis fonte LED claritatem per WiFi moduli, et subsidium vocis terrorem.

Programma lineamenta:

1. Accipe T5L chip ad alta frequentia, AD analog sampling stabilis est, et error parvus est;

2. Support TYPE C directe cohaeret cum PC ad debugging et programmatis incendii;

3. Suscipe celsitatem nuclei interfaciei OS, 16bit portum parallelum;UI core PWM portum, AD portum educunt, humilis sumptus applicationis consilium, nihil opus addito MCU addere;

4. Support WiFi, Bluetooth remote control;

5. Support 5~12V DC intentione ampla et amplis input

1,1 Schema diagram

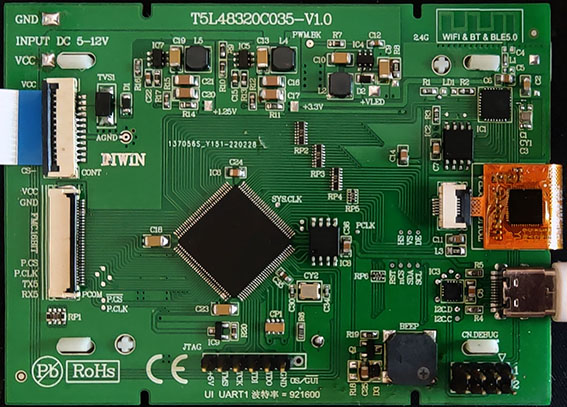

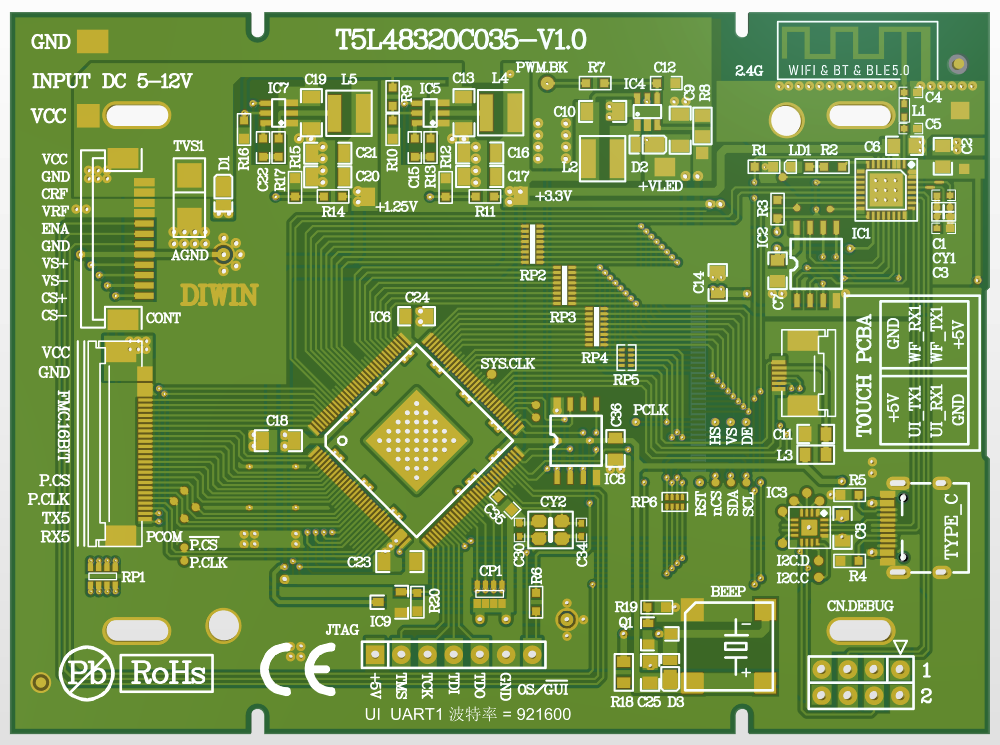

1.2 PCB tabula

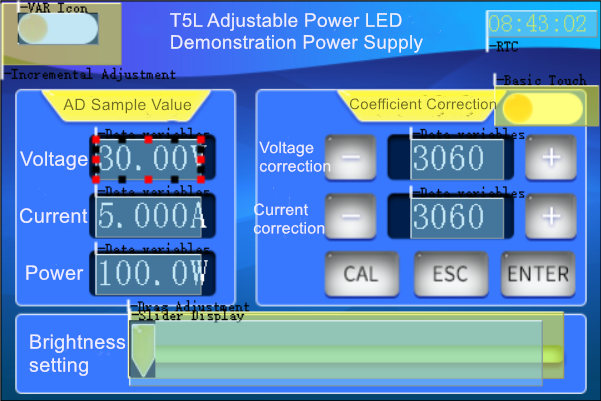

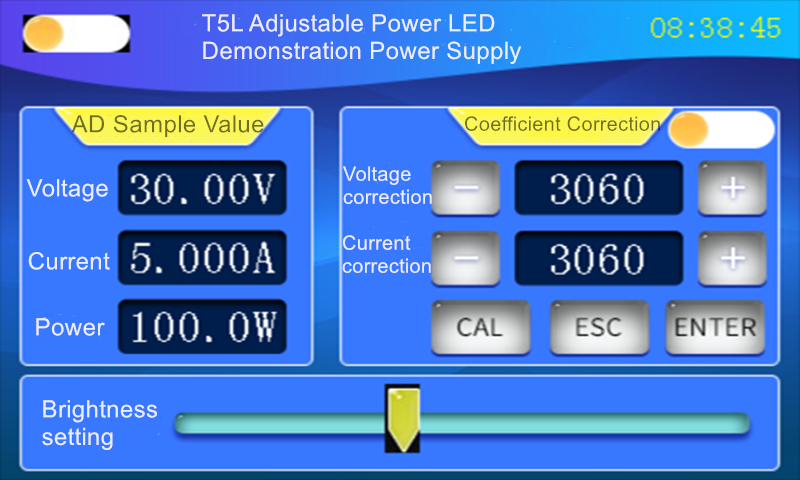

1.3 User interface

pudor introductio

1)Hardware circuitu design

1.4 T5L48320C035 circuitus diagram

1. MCU logicae potentia supplet 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU core potestas suppeditat 1.25V: C23, C24;

3. MCU analogiae potentiae copia 3.3V: C35 est analogiae potentiae copia pro MCU.Cum typothetarum, nucleus 1.25V terra et logica terra coniungi possunt, terra autem analogia separari debet.Analoga humus et terra digitalis colligenda sunt ad polum negativum LDO output magnum capacitorem, et polus positivus analogus etiam ad polum positivi LDO capacitoris magni colligendum, ita ut sonitus AD sampling minimatur.

4. AD analog signum acquisitio circuli: CP1 est AD analogum input filter capacitor.Ut errorem sampling reducere, analogum humus et digitales ratio MCU independenter separantur.Polus negativus CP1 coniungi debet cum analogo fundamento MCU cum impedimento minimo, & duo capaciores paralleli oscillatoris cristallini MCU ad terram analogam connexae sunt.

5. Buzzer circuit: C25 est potestas copia capacitor pro BOMBINATOR.BOMBINATOR fabrica inductiva est, et in operatione vena culmen erit.Ad apicem reducendum, necesse est MOS currentem stridore reducere ut MOS tubum in regione lineari operari faciat, et ambitum designet ut in mode transitum operetur.Nota quod R18 in parallelis ad utrumque finem BOMBINATOR coniungi debet, ut sonum qualitatis buzzer accommodet, et sonum crispum et amoenum faciat bombo.

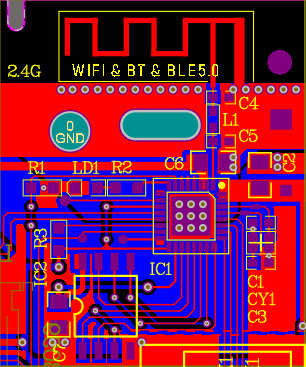

6. Circuitus WiFi: WiFi chip sampling ESP32-C, cum WiFi+Bluetooth+BLE.On wiring, the RF the power ground and the signal ground are separate.

1.5 WiFi circuit design

In superiore figura, superior pars efficiens aeris est vis terrae fasciae.Antennae reflexio WiFi antennae humus ansa magnam aream habere debet ad potentiae terrae, et punctum collectionis terrae potentiae est polus negativus C6.Reflexus currenti provideri debet inter antennae potentiae et WiFi, ut vestis aenea sub antenna WiFi esse debet.Longitudo coatingis aeris excedit antennae extensionem longitudinem WiFi, et extensio sensibilitatem WiFi augebit;designandum ad polum negativum C2.Magna area aeris potest protegere strepitum antennis WiFi radiorum causatum.Causae 2 aeris in strato ima separantur et ad medium codex ESP32-C per vias colligentur.Potentia RF loci inferiori impedimento indiget quam ansa usitata, ideo sunt 6 vias a terra potentiae ad codex chippis ut satis humilis impedimentum curet.Terra ansa oscillatoris crystalli oscillatoris RF vim per illam fluentem habere non potest, alioquin oscillator crystalli frequentiam jitterarum generabit, et WiFi frequentia cinguli notitias mittere et accipere non poterunt.

7. Backlight DUXERIT potestas copia ambitum: SOT23-6LED coegi chip sampling.Copia potentiae DC/DC ad DUXERIT independenter ansam format, et DC/DC humus ad 3.3V LOD humum coniungitur.Cum PWM2 nucleus portus designatus est, 600K signum PWM outponit, et RC additur ut PWM output ut ON/OFF imperium.

8. Voltage input range: two DC/DC step-downs are designed.Nota R13 et R17 resistentes in circulo DC/DC omitti non posse.Duo DC/DC astulae ad 18V input sustinent, quae copiae potentiae externae convenit.

9. USB TYPE C debug portum: TYPE C inplenda et inplenda est ante et retro.Deinceps insertio communicat cum WIFI chip ESP32-C ut chip WIFI communicat;e converso insertio communicat cum XR21V1410IL16 ad programmata T5L.TYPE c 5V copia virtutis sustinet.

10. Communicatio portus parallelis: T5L nucleus multos habet liberas IO portus, et 16bit communicatio parallela portus designari potest.Protocollo parallelo portui ST ARM FMC deducta, synchronum legi et scribere sustinet.

11. LCM RGB summa velocitas instrumenti interfaciei: T5L RGB output directe coniungitur cum LCM RGB, et quiddam resistentiae in medio additur ad impedimentum aquae lanitae LCM reducendae.Cum wiring, longitudinem RGB interfaciei connexionis minuunt, praesertim signum PCLK, et RGB interfaciem PCLK, HS, VS, DE puncta examinis auge;SPI portus screen iungitur P2.4~P2.7 portubus T5L, quod commodum est ad designandum exactoris tegimen.Educ RST, nCS, SDA, SCI probationes puncta ut faciliorem reddant evolutionem programmatis subiectae.

(2) DGUS interface

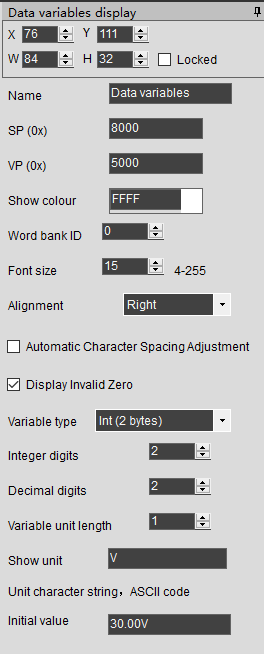

1.6 Data variabilis ostentationem imperium

(3) OS

-------------- DGUS legere et scribere forma

typedef instruere

{

u16 addr;// III 16bit variabilis oratio

u8 datLen;// 8bitdata longitudo

u8 *pBuf;// 8bit notitia indicatorum

} UI_packTypeDef;// DGUS legere et scribere facis

//---------------- varia ostentationem imperium

typedef instruere

{

u16 VP;

u16 X;

u16 Y;

u16 Color;

u8 Lib_ID;

u8 FontSize;

u8 Algnment;

u8 IntNum;

u8 DecNum;

u8 Type;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;// data variabilis descriptio structurae

typedef instruere

{

Number_spTypeDef sp;// define SP description indicatorum

UI_packTypeDef spPack;// define SP variabilis DGUS legere et scribere sarcina

UI_packTypeDef vpPack;// define up variabilis DGUS legere et scribere sarcina

} Number_HandleTypeDef;// data variabilis structura

Cum praecedente notitia variabilis ansa definitionis.Deinceps, variabilis pro intentione sampling ostentus definire:

Number_HandleTypeDef Hsample;

u16 voltage_sample;

Primo, munus initialization exequi

NumberSP_Init(&Hsample, voltage_sample, 0×8000);//0×8000 hic est descriptio monstratoris

//-- Data variabilis ostensio SP monstratorem structuram initialization--

inanis NumberSP_Init(Number_HandleTypeDef *numerus,u8 *value,u16 numberAddr)

{

number->spPack.addr = numberAddr;

number->spPack.datLen = sizeof(number->sp);

number->spPack.pBuf = (u8*)&number->sp;

Read_Dgus(&number->spPack);

number->vpPack.addr = number->sp.VP;

switch (number->sp.Type) // Data longitudo variabilis, sponte seligitur secundum notas variabiles in DGUS interface designatas.

{

causam 0:

causam V;

number->vpPack.datLen = 2;

frangere;

casus I;

casus II;

casus III;

casus VI;

number->vpPack.datLen = 4;

casus 4:

number->vpPack.datLen = 8;

frangere;

}

number->vpPack.pBuf = value;

}

Post initialization, Hsample.sp monstrator est descriptio notitiarum variabilium voltagenarum sampling;Hsample.spPack est index communicationis inter nucleum OS et UI voltage sampling notitia variabilis per munus interfaciei DGUS;Hsample.vpPack est attributum mutandi voltages sampling notitiarum variabilium, ut font Colores, etc. ad nucleum UI per functionem interfaciei DGUS transmittuntur.Hsample.vpPack.addr est intentione sampling notationis variabilis electronica, quae ab ipso munere initialization consecuta est.Cum electronica variabilis vel variabilis notitia generis in DGUS interfaciem mutas, opus non est in core synchrone OS inscriptionem variabilem renovare.Postquam nucleus OS voltage_sample variabilis computat, solum opus est ut Write_Dgus(&Hsample.vpPack) munus suum renovare debet.Nihil opus est ad DGUS transmissionem condere voltage_sample.

Post tempus: Iun-15-2022